基于UPF的低功耗数字后端设计技术是芯片设计中非常重要的一环,现在越来越多的公司和岗位对此有要求。如果想从事相关领域的工作,掌握基于UPF的低功耗数字后端设计技术是非常有必要的!本次,E课网特推出全新的《基于UPF的低功耗数字后端设计实训课》,课程采用基于矿机的后端项目,项目实践从前端的RTL代码,经过逻辑综合,布局布线和静态时序分析,帮助大家掌握基于UPF的低功耗后端实现技术,完成进阶之路!快快报名参加吧~一、项目介绍

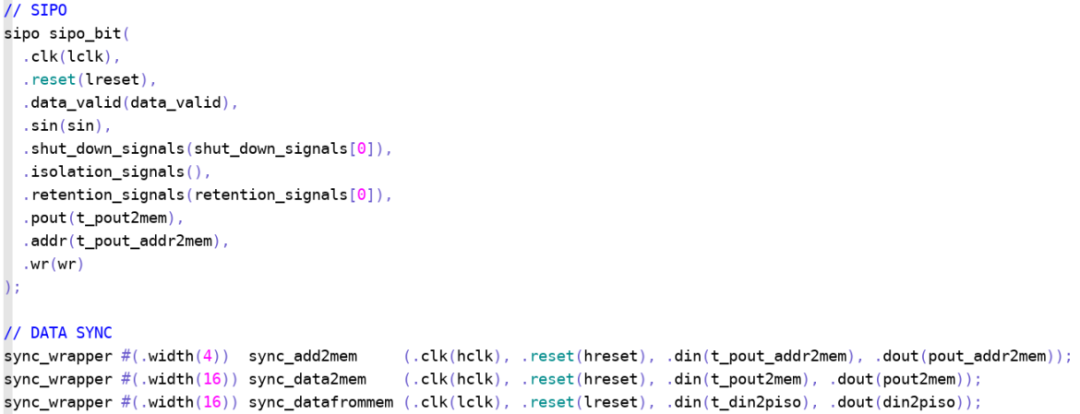

工艺介绍:28nm工艺;RTL代码示例:

UPF代码示例:

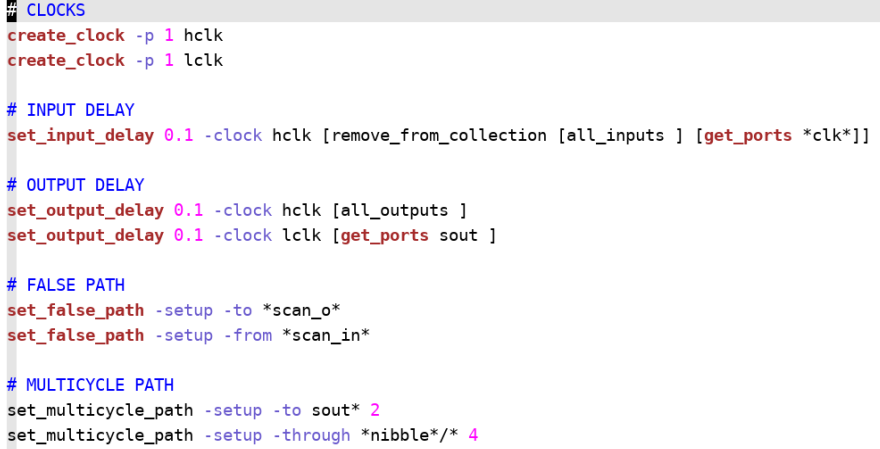

DC:sdc代码示例:

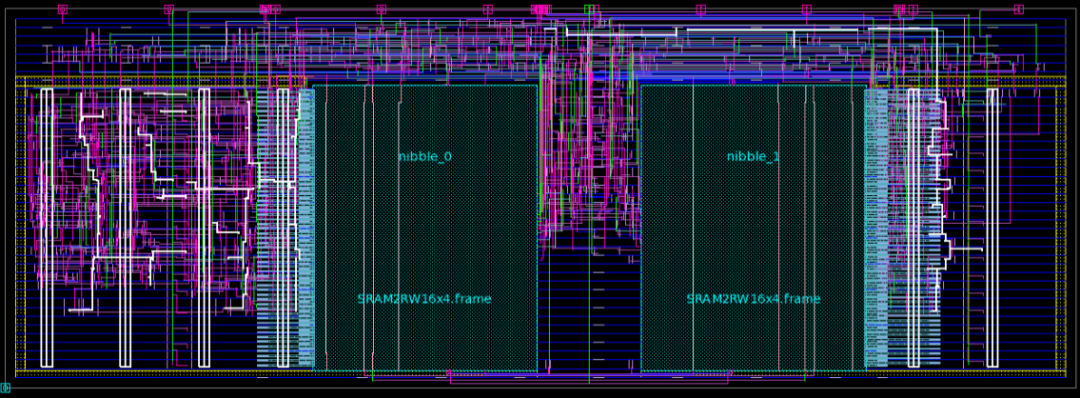

PR::

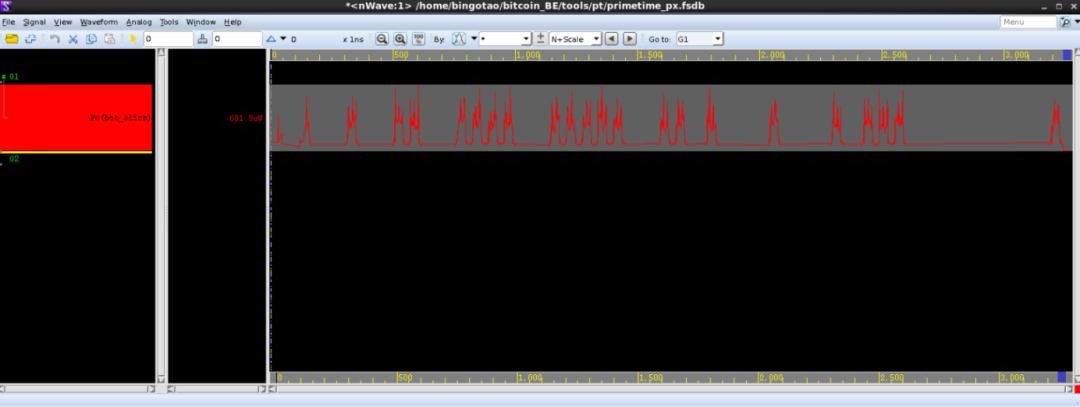

PT PX功耗峰值分析:

二、低功耗简介

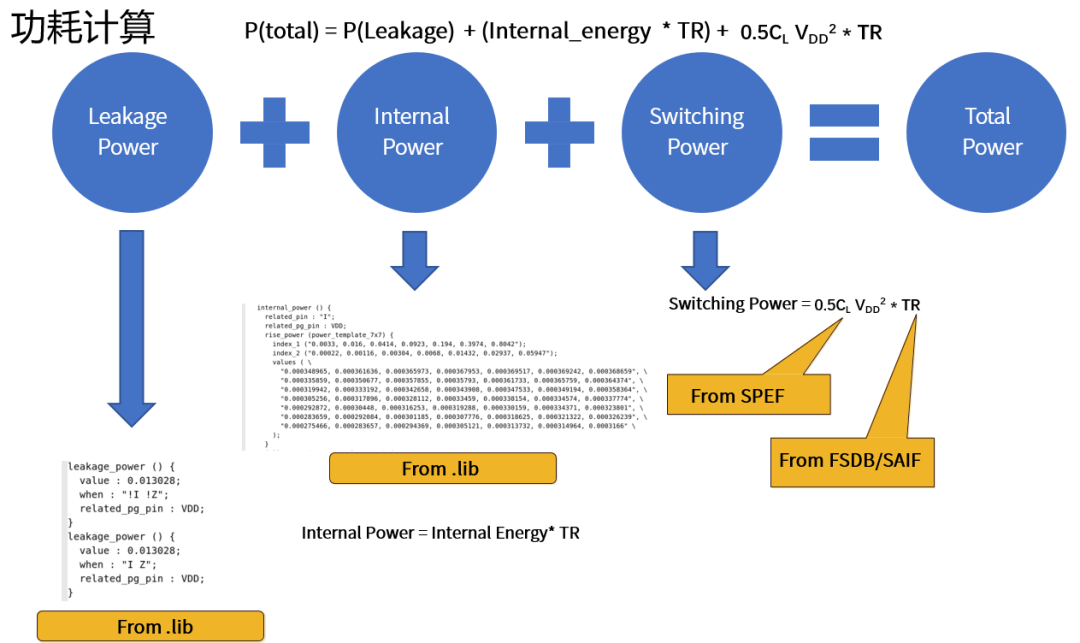

现如今,手机电脑等电子设备已经成为了大家日常生活中的必需品,而我们最关心的,除了性能之外,可能就是它们的续航了。因为电子设备如果功耗过大,就会产生更多的热量,设备过热便会影响器件工作,手机电脑会因此卡顿。因此,低功耗设计就显得至关重要。CMOS电路中功耗分为静态功耗和动态功耗,动态功耗是由内部功耗和开关功耗组成的。其中动态功耗的分析依赖于前端VCS功能仿真提供的包含Switching Activity信息的FSDB波形文件或者SAIF文件。

在数字芯片设计中,低功耗方法学是一项非常重要的学习内容,可以利用UPF对power domain进行系统性的管理,从而提高芯片的续航能力。

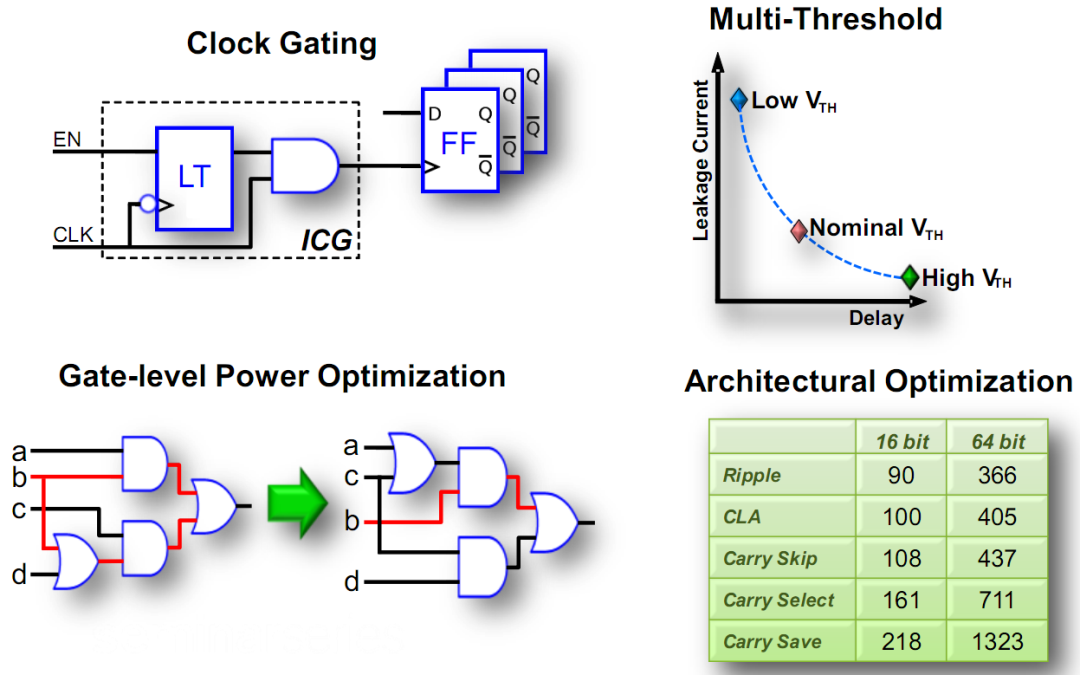

芯片设计中主流的低功耗技术:

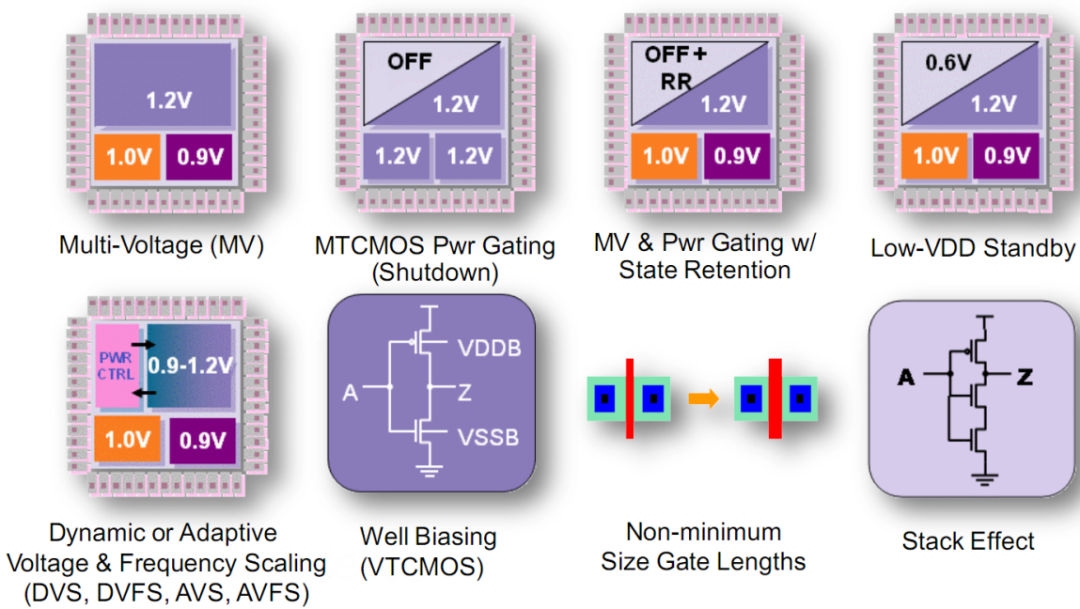

数字后端中多电压域:

带UPF的低功耗设计流程中包括了前端VCS-NLP功能仿真,后端VC LP静态验证,以及在DC综合和ICC2布局布线中低功耗单元的插入,例如level shifter,isolation cell,retention cell和power switch等。Signoff阶段的Formality逻辑等价性检查以及PTPX功耗分析等。

三、UPF简介

UPF(Unified Power Format)是通用的电源格式,是一组TCL语言的集合,用来描述芯片设计中的低功耗意图。UPF可以描述芯片工作的“电特性”,包括工作电压、电压的开关、低功耗cell插入的策略和芯片的power state等,UPF可以应用在设计、分析、验证和实现流程中。低功耗设计流程中加入UPF可以保证功耗意图在IC设计中的一致性,使低功耗意图在仿真、综合、一致性检查和设计验证环节更容易实现。

UPF历史UPF的运用贯穿低功耗设计的始终,包括仿真验证、逻辑综合、物理实现、等价性验证和最终签核的过程。综合阶段会读入RTL文件和初始UPF文件,产生门级网表及综合后的UPF文件,该UPF文件不仅包括初始UPF信息,并且还包括了在综合过程中插入的低功耗单元。物理实现阶段是读入综合产生的网表和UPF,执行布局布线后,生成包含整个电源信息的网表和布局布线的UPF,该UPF包含初始UPF信息,并且还包括了插入的低功耗单元之间的电源连接关系。

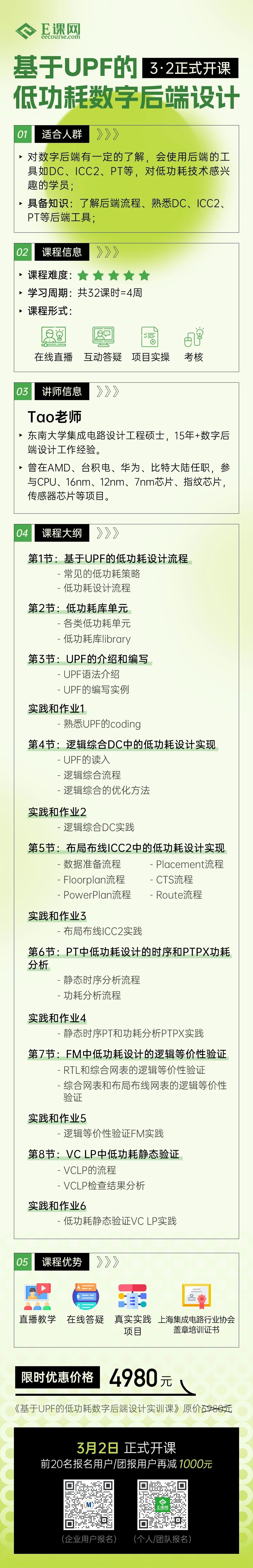

四、课程简介

五、课程亮点

1、精讲精练:科学配备授课内容,讲练结合更高效。

2、名师上阵:大厂名师亲自带做项目,氛围感拉满。

3、助教督学:小班教学模式,助教全程贴心辅助。

4、直播答疑:一对一实时互动,针对性解决问题。

5、阶段测试:巩固前期学习成果,及时帮助查漏补缺。

6、项目实践:新增矿机项目,innovus中低功耗实现lab,理论结合实际工程授课等。

7、双重认证:考核通过即可获得“摩尔精英E课网IC能力培训证书”,成绩优异的同学还可获得上海半导体行业协会认证版证书。

8、价格优惠:限时限量发放优惠券,组团报名价格更优惠。

六、培训证书

课程结束后进行考核,考核一旦通过,将为大家颁发由上海市集成电路行业协会(SICA)与E课网联合认证的培训证书,单张证书拥有唯一的验证码,可在网站上直接查询!重要通知!E课网培训证书含金量升级,上海市集成电路行业协会加持认证!

致老师的一封信:https://www.henkao.com/xuexi/2488.html

竣工验*报告:https://www.henkao.com/zhichang/1870.html

黄秋葵的*法:https://www.henkao.com/yinshi/435.html

二年级家长会班主任发言稿:https://www.henkao.com/xuexi/2026.html

6个月*成长寄语:https://www.henkao.com/qinggan/1666.html

运动会加油稿:https://www.henkao.com/xuexi/1129.html

公司实习报告:https://www.henkao.com/zhichang/2523.html

廉政心得:https://www.henkao.com/zhichang/1964.html

姐妹聚会的说说:https://www.henkao.com/qinggan/1613.html

介绍自己的英语作文:https://www.henkao.com/xuexi/2465.html

打动人心的爱情句子:https://www.henkao.com/qinggan/648.html

女生游戏名字:https://www.henkao.com/wangluo/1555.html

黄河大合唱听后感:https://www.henkao.com/xuexi/2594.html

暗示一切重新*始的个性网名:https://www.henkao.com/wangluo/778.html

情侣网名唯美:https://www.henkao.com/wangluo/1304.html

一听就很干净的名字:https://www.henkao.com/yuedu/1477.html

唯美网名:https://www.henkao.com/wangluo/742.html

国旗下讲话:https://www.henkao.com/xuexi/2667.html

小学语文质量分析:https://www.henkao.com/zhichang/2406.html

文员职责:https://www.henkao.com/zhichang/2029.html

英雄联盟ID:https://www.henkao.com/wangluo/1271.html

打12315投诉后悔了:https://www.henkao.com/yuedu/522.html

怎么判断狮子座动心了:https://www.henkao.com/xingzuo/1024.html

安全隐患排查报告:https://www.henkao.com/zhichang/1966.html

好的句子:https://www.henkao.com/xuexi/446.html

搞笑的昵称:https://www.henkao.com/wangluo/1387.html

qq炫舞名字:https://www.henkao.com/wangluo/1446.html

关于老师的作文600字:https://www.henkao.com/xuexi/2556.html

各自安好不再打扰的说说:https://www.henkao.com/qinggan/904.html