相信很多ICer们在Light芯片的过程中无论前后端都听过DFT设计测试,DFT全称Design for Test(即可靠性设计),众所周知,测试的目的是为了保证芯片成品的质量以及功能逻辑的可靠性的必须 措施。在十年前,芯片的测试还多为板级仿真波形测试,即用示波器等硬件设备去勘测芯片的逻辑功能 是否正常,但是随着芯片复杂性的提升以及功能逻辑数目的增加,基础的板级测试已经不能保证整体的 覆盖率和最后的良率了,芯片测试也逐渐覆盖到设计制造的全流程当中。小编将从设计流程以及verilog HDL,故障和缺陷模型的建立,故障仿真应用与方法,测试向量生 成方法及算法,确定性测试生成算法,扫描法进行测试电路设计,逻辑内建自测试,测试压缩,MBIST 测试存储器等11章出发,从理论以及实际上讲解DFT设计流程以及注意项。首先要明白为什么要进行芯片测试,在数字系统中又到底在测试什么?答案是:测试是为了发现成 品芯片或者器件的物理缺陷(如下图),数字系统中测试的为各逻辑单元的功能/PIN的完好性。

图1 晶圆上流片失败的物理缺陷图

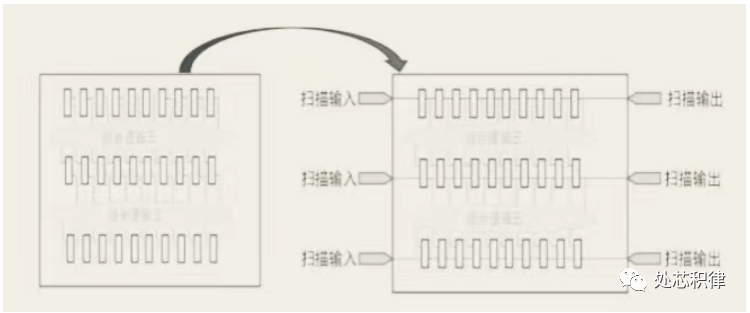

不难看出,从左往右造成缺陷的原因依次为:第一个落了灰尘造成short,第二个金属线open,第三 个也是短路,两根金属搭在一块,第四个下方金属/OD层的通孔断了,第五个缺陷光刻刻蚀错了。这种 的缺陷在TO的过程中是致命的,也是需要DFT工程师提前去排除的。实际上在DFT测试过程中最常用的 测试为全扫描测试,即将时序逻辑替换成带SI,SE端的SDFF(等效于在普通移位寄存器DFF的D端连一 个MUX,即最基础的扫描单元SDFF),然后将时序逻辑串起来,以便对组合逻辑进行测试。

图2 串链通过Input&Out port来监测输出

全扫描测试可以显著的增加芯片的可测性,而DFT扫描链测试的基本原理就是可观可控,什么是可观 可控呢?说的通俗一点就是“黑盒子”,在具体的芯片设计中不可能去调整具体logic的PIN的直接输入,也 不能直接监测对应logic的直接输出,DFT工程师是通过调整测试/功能模式,在芯片的Input PIN控制输 入,而在Output Pin控制输出,通过控制输入PIN的信号,监测输出PIN的信号,来达到“可控可观”的目 的。

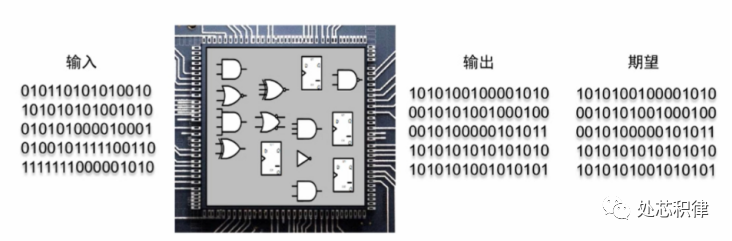

图3 通过控制芯片引脚的输入根据输出判断是否发生故障

可以看出在给定一串复杂多位二进制信号后,经过内部组合逻辑和时序逻辑的转换,在不同周期可 以得到一个对应输出引脚的输出值,在理论上又有个期望值,若期望值和输出值不符,则可以通过在测 试模式下调整输入准确的找到问题的所在。这么解释可能有点宽泛,下面我们举个用来测试XOR的一个module的例子(并行串出结构),DFT 扫描链是如何通过控制SI,SO,SE端来实现输入可观(SI)输出可测(SO)的,首先在SI第一周期输入信 号1,此时第一个周期三拍的状态分别为100,然后这个时候第二拍传递给XOR上方的INPUT PIN的值为 1,第一拍传递给下方的INPUT PIN的值为0,按照1^0 =1的异或逻辑来说,如果是功能模式状态下,第 二个时钟周期应该会输出1,这样第三拍第三周期怎么都会输出1,无论是功能还是测试模式。但是假设 XOR的Output Pin floating了的话,在第二周期切功能模式,则在第三周期第三拍会收到X态的信号,和 预期的1值不符合,这就完成了一个简单的输入可观,输出可控的DFT扫描测试。

图4 三扫描测试XOR的原理图

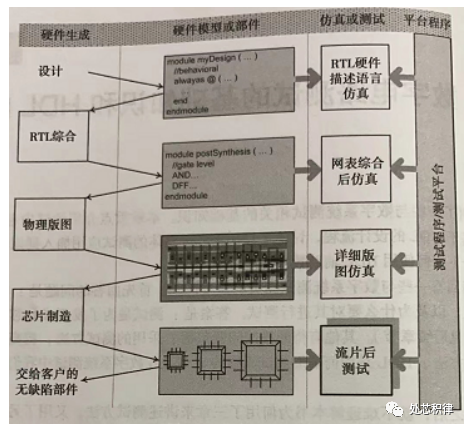

数字系统的制造流程,是以设计使用VHDL/Verilog HDL描述其设计开始,并以制造装运各部件交付 客户为终点,接下来小编来讲解下DFT工程师在整个设计流程当中是如何参与测试,并在不同阶段进行 仿真测试的:

RTL设计流程仿真:这一流程主要依赖一些前端工具如VCS,Verdi,MSIM等等,通过对输入的可 综合的顶层verilog互连模型的仿真来检查设计的功能是否正常,为了方便分析设计行为,平台可以 通过注入设计错误即激励来预测该设计在非预期环境下的行为。这一工作在fabless公司通常由验证 工程师来实现完成,在基于Spec进行检查的时候,验证和基于断言的验证方法非常有效,各种验证 方法可以是HDL仿真器的一部分,也可以作为独立程序使用

RTL综合:RTL综合实际上就是在APR之前,将可综合RTL代码转换为门级Netlist网表的过程(此过 程也要插入DFT测试逻辑),在综合完成后,需要对生成的RTL代码进行Formal形式验证,并利用 HDL仿真工具对Netlist进行后仿测试,在仿真的过程中,要检查delay问题,竞争与冒险,时钟速 度以及综合工具对RTL设计错误判断所导致的综合错误。一般来说,需要保证综合过后的网表与综 合前的RTL代码描述一致。

物理版图:后端APR完后吐出的GDS版图通过对IP以及std cell,dummy的merge后,引入spi mod进行DRC,ANT,LVS check,当连线的长度,宽度以及晶体管的大小等DRC rule里规定的内 容都通过仿真检查后,版图GDS就能用于制造芯片了。

芯片制造:相对于图1-1中其他三种形式的测试而言,在生成测试中则有物理器件(要么硬件,要 么测试设备)执行测试。但是,预期响应均全部或部分基于前几个设计阶段已完成测试所获得的经 验。在理想状态下,用于流片后方框上面的三个方框的同一测试平台应转换为运行在测试成品部件 的测试设备上的测试程序。

流片后测试:流片后测试主要包括测试机,应用测试结果,测试类型等等,DFT工程师将能获得的 某个电路的预期响应的模型称为无故障模型/黄金模型。首先从ATE测试机台说起,无论何种机台, 测试机均指将测试向量应用于被测器件,收集北侧器件响应并与预期数据进行比较的器件或设备。输入生成的测试向量给被测器件DUT,测试机台回收输出的响应,即测试机只管被测器件(DUT)的 输入(测试向量),以及输出(测试响应)。应用测试结果即在发现制造缺陷后,对测试器件/芯片的处 理,存在灾难型缺陷的芯片一般会被丢弃,性能或质量不行的则会当成残次品低价出售。测试类型 多种多样:其中包括内外部测试,联机测试,脱机测试,并发测试,全速测试,DC测试等等,不同 测试方法的区别在于对可测器件芯片测试速度测试频率测试模式的不同调整。

图5 各阶段仿真测试流程

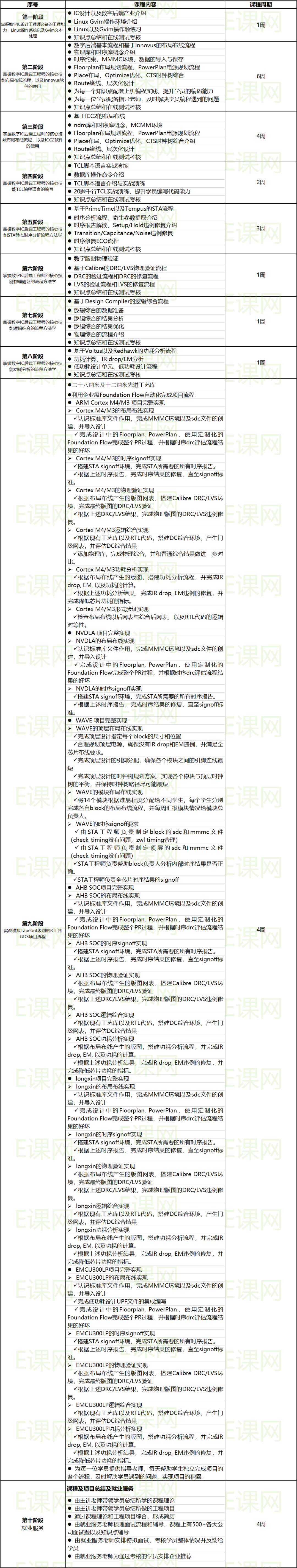

好了,到这里小编对DFT数字设计流程的介绍就讲到这里了。E课网《数字后端设计工程师就业班》即将开课!快来一起学习吧~

【项目介绍】

基于精简指令集的CPU的数字后端设计

基于SoC芯片的数字后端设计

【课程大纲】

公布对象的文案短句:https://www.nanss.com/wenan/2236.html

感恩老师作文:https://www.nanss.com/xuexi/2173.html

等待春天的心情:https://www.nanss.com/yuedu/2044.html

天冷加衣暖心句子:https://www.nanss.com/yulu/2107.html

史记读后感:https://www.nanss.com/xuexi/2135.html

愿亲人在天堂安好唯美句子:https://www.nanss.com/yulu/2041.html

高考完祝福语:https://www.nanss.com/xuexi/2047.html

爱的教育读后感500字:https://www.nanss.com/xuexi/2127.html

党务工作总结:https://www.nanss.com/gongzuo/2106.html

激励上进正能量句子:https://www.nanss.com/wenan/2495.html

工作转正申请书:https://www.nanss.com/gongzuo/2303.html

美团好评50字通用评论:https://www.nanss.com/shenghuo/2325.html

优秀学生申请书:https://www.nanss.com/xuexi/2453.html

青年志愿者活动方案:https://www.nanss.com/gongzuo/2100.html

让人惹不起的网名:https://www.nanss.com/mingcheng/2351.html

写植物的作文三年级:https://www.nanss.com/xuexi/2068.html

爱岗敬业的文章:https://www.nanss.com/gongzuo/2029.html

我的动物朋友作文400字四年级下册:https://www.nanss.com/xuexi/2473.html

奖项名称:https://www.nanss.com/shenghuo/2052.html

这段木头里一定有虫作文:https://www.nanss.com/xuexi/2025.html

*到女儿礼物的心情说说:https://www.nanss.com/wenan/2251.html

理想作文:https://www.nanss.com/xuexi/2180.html

节约用水倡议书:https://www.nanss.com/shenghuo/2296.html

一句话餐饮经典语录:https://www.nanss.com/gongzuo/2283.html

高中读后感:https://www.nanss.com/xuexi/2126.html

善意的谎言作文:https://www.nanss.com/xuexi/2171.html

朋友圈水果配文字简短:https://www.nanss.com/wenan/2321.html

植物作文:https://www.nanss.com/xuexi/2196.html

压抑了很久的心情终于释放了:https://www.nanss.com/wenan/2242.html