一.岗位介绍

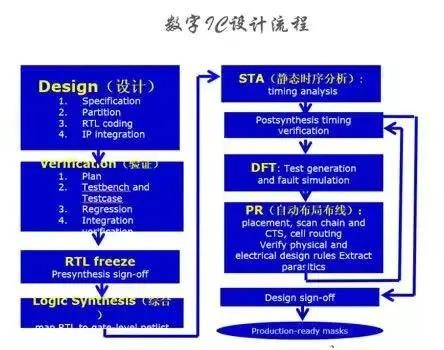

数字验证处于数字IC设计流程的前端,属于数字IC设计类岗位的一种。随着芯片规模不断加大,在IC设计过程中验证的复杂度也进一步加到,需要的用到的岗位人数也越来越多,很多大公司,数字前端设计工程师与验证工程师的比例已经达到1:3。

数字验证主要分成几种层次的验证:IP level,unit level,fullchip/SoC level,gate level,硬件加速仿真等。人才的需求量进一步加大,这也是现阶段数字验证工程师招聘量巨大的原因。

二.主要干啥?

1. 阅读各种SPEC

最重要的一份spec是design spec,就是和你一起合作的好基友设计工程师写的设计文档,比如下面这种:

其中需要重点了解的内容是:

- fetures:这个模块需要支持的性能列表。

- IO ports:这个模块对外的IO端口。

- operation mode:这个模块的主要工作模式。

除了这份详细的设计文档之外,如果这个IP需要用到很多协议,那你自然还要去阅读一些协议文档咯,比如AMBA总线协议,MIPI协议,DDR协议等。

2. 撰写verification spec

公司里面,工程师做事情之前都需要出一份详细的文档,验证工程师也不例外,你要出的文档叫做verification spec,其中主要的内容包括:

-

验证平台架构:以UVM验证平台为例。

实际上,现在IC行业内,很多公司的验证环境都不尽相同,比如有纯C/C++的环境,有纯UVM的环境,有UVM+C++的环境,甚至还有systemc的环境。总的来说,现在的趋势都是在往UVM的验证环境上转。

-

测试用例(test plan)

test plan的出炉是一个高质量的工作,因为它决定了你验证的工作量,最重要是它决定了你验证的完整度。验证工程师的终极目标就是:覆盖所有的情况,不放过任何一个bug。

这份东西需要你和designer反复的详细讨论,在后面的过程中,还需要进一步的优化补充这份文档。

3. 码代码,搭建验证环境

verification spec完成之后,接下来就要开始码代码了,使用各种验证语言去搭建验证环境,常用的验证语言有C/C++,systemC,systemverilog。

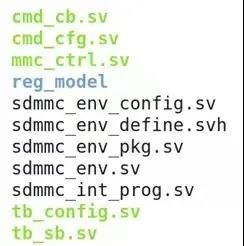

以现在主流的UVM验证平台为例:大概要去码完类似这样的文件。

好的验证平台是检验工程师优秀的一个重要标准,要考虑实用性、扩展性。

好消息是,公司里面有很多已有的验证环境,你可以模仿,在已有的基础上进行修改就可以了。

4. 创建test cases

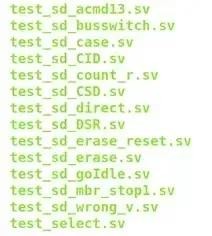

根据前面完成的详细test plan去创建验证需要用的test cases,每家公司对test cases的命名有一定规则,比如长这样的:

有些公司就直接用数字来给test cases命名。还有些公司,直接用脚本来生成test cases,只要把关键的一些设置调好,用脚本一刷,case就全部生成了。

当然每种创建cases的方法各有优缺点,你进去公司之后,也只能入乡随俗。

5. debug

验证环境和测试用例都搭建好了,下一步重点就是仿真和debug了。前面搭环境的时间其实大概只占20%,debug才是最花时间的。

仿真所用到的工具主要有:

- mentor:questasim

- cadence:NC-sim

- synopsys:VCS

几款工具一个比一个好,当然价格也是一个比一个贵。工欲善其事必先利其器,要想提高你的仿真和debug效率,工具里面好的功能也要好好研究下的。

debug主要目的是寻找RTL的bug,当然前面搭建的验证平台也会存在很多bug,最终的目标就是所有的test cases都能完全仿真通过。

最主要的debug手段有:

- 查看log文件:仿真结束会生成很多结果文件。

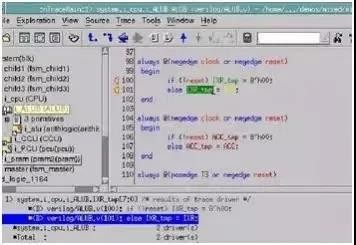

- 看波形:最常用工具就是verdi了。

每家公司对于验证工程师debug的要求不尽相同,比如AMD,就要求验证工程师能找到最终的root cause,而大多数公司只要求验证工程师能基本定位,然后designer去详细debug。

6. regression和coverage

到了项目的后期,所有的case都pass过了,并且比较稳定了,下一步就要开始跑regression和coverage了。

所谓regression就是把所有的case同时跑一遍,因为大多数case里面会有很多random的机制,所以在不断重跑的过程中,会随机性的出现case fail。这也是regression的主要目的,就是抓出那些极端情况下出现的debug。

coverage主要包括code coverage和function coverage等,每家公司的要求都不尽相同。

每家公司跑regression和coverage都会使用脚本来完成,怎么高效顺利跑完,是最关键的问题。最终的结果一般会以网页的形式呈现,直观明了。

7. support

前面属于验证工程师的常规任务差不多就完成了,support属于进阶版的。比如项目用的database出问题了,跑仿真用的flow碰到问题了,经常就会叫验证工程师去support,帮忙解决问题。

当然搞不定也无所谓,但是如果你经常能帮同事搞定这些问题,那你在公司的地位就能与日俱增,升职加薪就更有筹码了。

8. meeting

作为验证工程师,和其他工程师一样,经常还有无穷无尽的会议要开,各种review,各种讨论。

如果你作为会议组织者,请记得事先做好充分的准备噢,不然很容易被人鄙视的。

所以总结来说,最主要做的两件重要的事情是:编程 debug

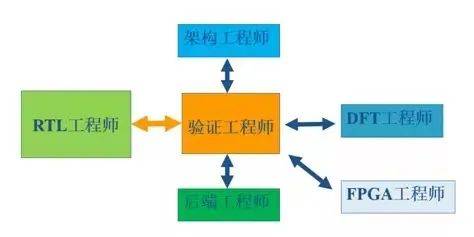

三.跟谁打交道?

验证工程师打交道最多的就是前端设计工程师(RTL设计工程师),一起讨论问题,经常一起debugcase,目的就是让写的verilog代码没有bug。

还经常需要和架构工程师打交道,去了解更多芯片的整体架构和features;如果你也负责后仿gatelevelsimulation的话,那还经常需要和后端工程师打交道,因为后仿的网表是他提供给你的;DFT工程师经常也会来找你,因为他也需要做测试和验证,很多时候他的验证平台经常就是从你的验证平台移植过去的;FPGA工程师也经常会打交道,因为FPGA验证也是数字验证的一种,你们会复用很多的测试用例,他也会经常来找你复现一些错误现场。

当然,如果你是在一家大公司的话,分工就非常明确,你也就不需要和这么多人打交道了,比如如果你只负责IP level的验证,那基本只要和前端设计工程师打交道就可以了。

四.得会啥?

现阶段由于数字验证的平台有很多种,主要的平台有:

- 纯verilog平台

- SystemC

- 纯C/C++ (CPU验证)

- 纯UVM平台

- UVM+C/C++平台

- 其他语言混合平台(Matlab等)

每种平台需要你掌握的技能不大一样,但比较主流的平台是3、4、5三种。一个初级工程师想全部掌握这些技能也很难,如果这些平台你都搭过,就变成老司机了。

由于验证工程师需要编程,所以掌握编程语言也是必须的,比如掌握下面知识就显得比较重要:

- Verilog

- C/C++

- Systemverilog

- UVM

另外,验证工程师经常需要流程的自动化,所以一些脚本语言也是必须的:

- Shell

- Makefile

- Perl

- Python

除了这些外,熟悉一些协议和架构,也是有很大帮助的,比如:

- ARM架构

- AXI/AHB协议

- MIPI协议

- DDR协议等等

所有的技术类岗位,主要看的两点就是:专业技能(skills)和项目经验(experience)。所以除了上面列的这些技能,你能实际做过一两个项目,哪怕是IP级别的验证项目,也是很重要的,尤其是做项目过程中积攒的debug经验。

如果你是在校学生,早几年懂验证的人极少,所以基本上你只要会verilog,可能就可以找到验证工程师的职位了。现在在校学生通过各种渠道(比如E课网),很多同学都掌握了上面的这些技能,甚至积累了一两个项目经验。会的人多了,招聘的要求也自然高一些了。

现阶段,数字验证工程师主要还是以招聘研究生为主,本科生招的很少。不过好消息是对专业的要求并不是很苛刻,并非集成电路方向不可,只要你掌握了上面的这些技能,哪怕不相关专业,比如材料、物理、自动化、机械等专业,也是可以成功应聘。

学历本科的同学也不要气馁,有工作经验的本科生,还是可以找到验证工程师的职位的,而且有很多成功的例子的。毕业学校一般的同学也不要气馁,985高校毕业,肯定是有优势的,但毕竟每年毕业生不多,在现在IC行业整体缺人的大背景下,依然会招收学校排名一般的学生的;当然前提还是一样,有专业技能(skills)和项目经验(experience)。

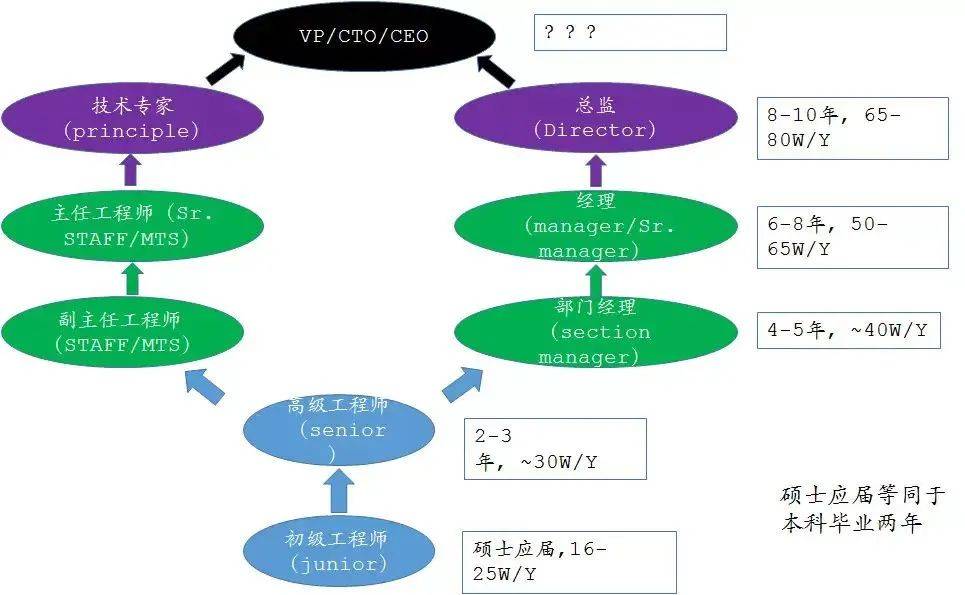

五.薪资和发展

这是最新2019届硕士应届生的薪水情况,最高已经可以拿到40万的年薪,一线城市平均薪资大概在25万左右,二三线城市稍微低一些。另外一个好消息是,国内现在在大力发展集成电路,所以最近几年薪资都在不断上涨,5年之内应该都还会保持这个趋势。

未来的发展,基本按照上图的发展阶梯来走,一些人会一直做技术,成为一名资深验证工程师,有些人会成为验证经理,做一些管理类的工作。好消息是大部分人只要一直做下去都能成为一名资深工程师(STAFF级别)或者经理,坏消息是只有极少数人能成为技术专家或者总监这个级别。

验证工程师干了很多年之后,有少数人也可以转,比如转去做架构工程师,去EDA公司做应用工程师(AE),要么就索性创业。总的来说,绝大多数验证工程师还是会一直做下去,毕竟这个岗位还算一个天花板不低的岗位。

六.工作环境

验证工程师的工作环境就比较简单,大多数时间就是待在办公室里面,面对电脑进行工作。一般配备两台电脑,一台台式机用来工作,一台笔记本用来看资料、处理邮件、文案处理等。

当然会议室是验证工程师经常要去的地方,各种会议、各种review都要在办公室完成,偶尔要少不了一些争吵和撕逼。

如果你在的公司,在全国甚至全球有很多site,偶尔也会需要出差。总的来说出差概率都比较少。当然,如果你是在设计服务公司做验证工程师,可能另当别论,一个项目完成之后可能会派到另外一家公司去。

验证工程师的工作强度还算可以,项目启动的时候相对轻松一些,越接近deadline,就会更忙,加班也是常事。当然,工作的强度还是依所在公司的性质来看,一般外企比较轻松,国内的公司就要辛苦很多。

验证工程师总的来说还算比较稳定,因为个人原因被裁员的概率很小,大多数情况都是公司的战略调整或者业务亏损,才会裁员。裁员也不要慌,大多数公司都提供不错的经济补偿,而且从现在的行情来看,很快就能找到新的工作。拿一笔可观的遣散费,立马去新公司上班,也算一种IC行业“福利”。

七.代表公司

数字验证工程师主要都是在IC设计公司,代表公司有:

外企大公司:

国内比较大的IC设计外企有Qualcomm、AMD、Nvidia、Marvel等,外企的待遇现在处于中上水平,但是工作强度相对小一些,论性价比来看的话,还是不错的选择。

国内大公司:

国内大公司有华为海思、紫光展锐、豪威科技等等,现在开的待遇都很不错,加上奖金远超外企,当然工作强度也是大很多,加班是常事,对于初级工程师来说可以考虑,辛苦一些,技术快速增长也是不错的。

EDA公司:

三大EDA公司和IC设计是密不可分的,synopsys、Cadence、Mentor三家外企待遇都还不错,性价比也还可以,还可以选择一些验证工具技术支持类的工作。

国内IC新锐:

最近几年,国内IC行情见涨,出现了很多土豪的芯片公司,薪资待遇也是开的非常高,比如大疆芯片设计部、寒武纪、比特大陆、地平线,规模也已经做的很大了。汇顶科技、ASR、兆易创新等也发展迅速。

国内IC初创公司:

还有一些成立不到两年的公司,手握大笔融资或者背靠金主,也是有很好的发展空间,比如平头哥半导体、燧原科技、天数智芯等。

从IC设计公司的分布来看,上海、北京是聚集地,工作机会最多,接下来是深圳、合肥、成都、西安、杭州、南京、苏州、武汉、广州、珠海、长沙。随着全国集成电路大战略的兴起,未来二三线城市的IC设计公司会越来越多的,对于想回家乡工作的小伙伴来说,是一个好消息。

E课网(www.eecourse.com)是摩尔精英旗下专业的集成电路教育平台,6年来致力于半导体行业高质量集成电路专业人才的培养。平台以集成电路企业岗位需求为导向,提供贴合企业环境的实训平台,通过线上线下的培训方式, 快速培养学员符合企业需求。

E课网拥有成熟的培训平台、完善的课程体系、强大的师资力量,规划中国半导体精品课程体系168门,涵盖整个集成电路产业链,并拥有4个线下实训基地。至今深度培养总人数15367人,为行业直接输送专业人才4476名。与143所高校建立深度合作关系,共举办企业专场IC培训240场。

- 还没有人评论,欢迎说说您的想法!