集成电路设计(Integrated Circuit,简称IC)一般分为数字IC设计、模拟IC设计和数模混合IC设计。数字IC设计一般又会进一步细分为前端设计(Front-end Design)和后端设计(Backend Design)。

前端数字IC工程师的工作一般包括电路规范(Spec.)的撰写,电路架构的设计,电路的实现以及验证、综合出符合要求的电路网表(netlist),最后按一定的工作规范要求提交netlist 给后端部门。

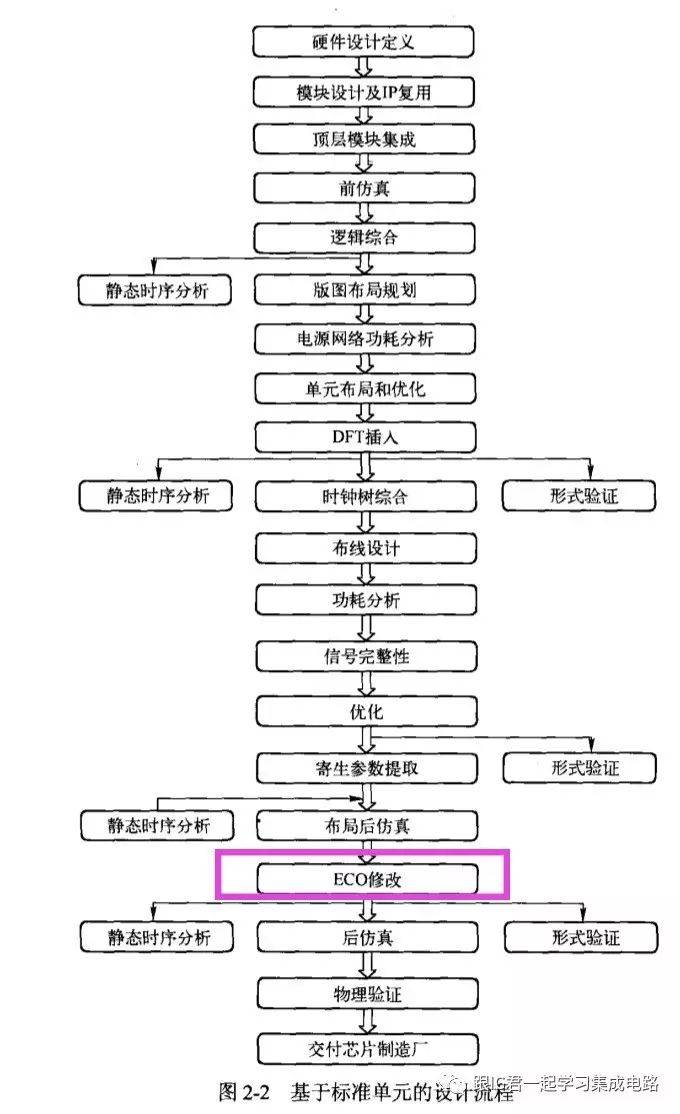

一个前端设计工程师的一天是怎样度过的呢? 早上九点打卡进入公司,到了公司座位后,多年养成的习惯是首先打开邮箱浏览一下邮件,看看昨天下班后有没有收到新的邮件,是否有比较紧急的事情需要优先处理的。今天还算不错,只有几封邮件,没有特别紧急的事情;不过有一封邮件是验证部门同事发的,邮件内容是我负责的一个IP昨天跑完的某个test case 有结果不对。 浏览完邮件后,就要对今天的工作任务做个简单的计划。每天早上花5~10分钟进行简单工作计划是很有必要的,既可以避免漏掉一些重要的事情,又可以清楚知道当天工作内容的轻重缓急。 今天主要有三件事:一、同仁负责的一个IP 有一个bug,需要对neltist 进行ECO 改掉,约好今天协助他一起解掉;二、前面说的负责IP 有test case 结果不对,需要今天跟验证部门的同事尽快沟通解决掉;三、今天下午四点有个技术讨论会,这是昨天就已经约好的会议。 工作计划安排好后,就是撸起袖子加油干了。首先介绍下ECO,ECO修改是基于标准单元设计流程中的一步。如下图所示:

E课网《数字前端设计工程师就业班》即将开课了!从理论基础到项目实战,由浅入深,帮助你全面掌握数字前端的专业技能和项目经验。目前已帮助2000+同学成功拿到高薪的数字设计offer!

【扫码咨询课程详情】

-

展望未来的励志句子:https://www.nanss.com/yulu/5963.html 归来仍是少年的上一句:https://www.nanss.com/xuexi/5539.html 高三家长寄语简短20字以内:https://www.nanss.com/xuexi/5579.html 家有儿子初长成美句:https://www.nanss.com/yulu/5662.html 班级目标:https://www.nanss.com/xuexi/5537.html 像造句三年级:https://www.nanss.com/xuexi/5864.html 坏脾气留给最亲近的人的说说:https://www.nanss.com/wenan/5654.html 丧气网名:https://www.nanss.com/mingcheng/5638.html 打篮球作文:https://www.nanss.com/xuexi/5757.html 越没本事的男人脾气越大的说说:https://www.nanss.com/wenan/5680.html b站昵称:https://www.nanss.com/mingcheng/5921.html 个人宣言:https://www.nanss.com/xuexi/5889.html 关于爱情的网名:https://www.nanss.com/mingcheng/5530.html 三年级学富五车造句:https://www.nanss.com/xuexi/5816.html 暴富祝福语:https://www.nanss.com/yulu/5942.html 网名搞笑:https://www.nanss.com/mingcheng/5518.html 带有青字最好听的网名:https://www.nanss.com/mingcheng/5846.html 怎么念都占便宜的网名:https://www.nanss.com/mingcheng/5982.html 感恩资助的句子:https://www.nanss.com/yulu/5953.html 三姐妹在一起的经典说说:https://www.nanss.com/wenan/5568.html 抑郁网名:https://www.nanss.com/mingcheng/5729.html 晒老公和*的句子:https://www.nanss.com/yulu/5656.html 春耕的优美句子:https://www.nanss.com/yulu/5952.html 心痛到撕心裂肺的网名繁体字:https://www.nanss.com/mingcheng/5676.html 微信视频号名字:https://www.nanss.com/mingcheng/5998.html 互利共赢的名言名句:https://www.nanss.com/xuexi/5841.html 18岁成人礼:https://www.nanss.com/xuexi/5550.html 史上最逗比的情侣名字:https://www.nanss.com/mingcheng/5740.html 带娃崩溃的句子发朋友圈:https://www.nanss.com/wenan/5830.html 幽默群名四个人:https://www.nanss.com/mingcheng/5782.html(0) 回复 (0)

展望未来的励志句子:https://www.nanss.com/yulu/5963.html 归来仍是少年的上一句:https://www.nanss.com/xuexi/5539.html 高三家长寄语简短20字以内:https://www.nanss.com/xuexi/5579.html 家有儿子初长成美句:https://www.nanss.com/yulu/5662.html 班级目标:https://www.nanss.com/xuexi/5537.html 像造句三年级:https://www.nanss.com/xuexi/5864.html 坏脾气留给最亲近的人的说说:https://www.nanss.com/wenan/5654.html 丧气网名:https://www.nanss.com/mingcheng/5638.html 打篮球作文:https://www.nanss.com/xuexi/5757.html 越没本事的男人脾气越大的说说:https://www.nanss.com/wenan/5680.html b站昵称:https://www.nanss.com/mingcheng/5921.html 个人宣言:https://www.nanss.com/xuexi/5889.html 关于爱情的网名:https://www.nanss.com/mingcheng/5530.html 三年级学富五车造句:https://www.nanss.com/xuexi/5816.html 暴富祝福语:https://www.nanss.com/yulu/5942.html 网名搞笑:https://www.nanss.com/mingcheng/5518.html 带有青字最好听的网名:https://www.nanss.com/mingcheng/5846.html 怎么念都占便宜的网名:https://www.nanss.com/mingcheng/5982.html 感恩资助的句子:https://www.nanss.com/yulu/5953.html 三姐妹在一起的经典说说:https://www.nanss.com/wenan/5568.html 抑郁网名:https://www.nanss.com/mingcheng/5729.html 晒老公和*的句子:https://www.nanss.com/yulu/5656.html 春耕的优美句子:https://www.nanss.com/yulu/5952.html 心痛到撕心裂肺的网名繁体字:https://www.nanss.com/mingcheng/5676.html 微信视频号名字:https://www.nanss.com/mingcheng/5998.html 互利共赢的名言名句:https://www.nanss.com/xuexi/5841.html 18岁成人礼:https://www.nanss.com/xuexi/5550.html 史上最逗比的情侣名字:https://www.nanss.com/mingcheng/5740.html 带娃崩溃的句子发朋友圈:https://www.nanss.com/wenan/5830.html 幽默群名四个人:https://www.nanss.com/mingcheng/5782.html(0) 回复 (0)